_Présentation_

L’activité du service Microélectronique de l’IP2I est d’étudier et concevoir des circuits intégrés pour les détecteurs de physique des particules, des hautes énergies, astro-particules ou médicales. Les instruments proposés par les physiciens nécessitent plus généralement des circuits analogiques bas bruit, basse consommation, multivoies, mais aussi des circuits entièrement numériques de traitement et de concentration de données. Les environnements des circuits sont en général contraints par des températures cryogéniques ou un taux de radiation élevée.

Le service fait appel à l’ensemble des techniques d’ingénierie microélectronique et collabore étroitement avec les services spécialisés dans ces techniques : mécanique, instrumentation, informatique et acquisition des données. Ses membres sont ingénieurs ou docteurs-ingénieurs, et spécialisés en architecture et conception de circuits intégrés.

La séquence type d’un projet passe par :

- Une discussion avec les responsables scientifiques et l’établissement des contraintes scientifiques et techniques,

- La conception / simulation au niveau schématique et le dessin des masques des circuits développés,

- La vérification du concept avec les responsables scientifiques,

- Le prototypage à travers des fonderies multi-projets,

- Le développement des bancs de test et des procédures d’assurance qualité,

- Le test des prototypes,

- l’amélioration des performances du concept,

- La pré-production (si nécessaire), la production et l’intégration au site de l’expérience scientifique.

Plus d’informations techniques sont également disponibles sur le site web de la Mi2i, pôle de compétences microélectronique du CNRS-NP ( IN2P3 )

_Activités_

Le service Microélectronique est ou fut impliqué dans les projets ci-dessous:

- DUNE

- CIC: CMS tracker concentrateur [2017-2024]

- R&T FASTIME

- R&T PICMIC

- R&T Tiix

- R&T SiGe [2022-2026]

- R&T Spider

Projets passés :

-

- Lojic130 [2018-2021]

-

- BB130

- CRONOTIC

- GAMHADRON

- HODOPIC

- ASIC Silicium

- Xtract réalisé à travers le pole MICRHAU (LPCA+IP2I) [2014-2018]

- MPTDC (circuit de Thèse) [2017-2020]

- DSM (Circuit de Thèse) [2010-2013]

- liste des publications

…

Description des projets :

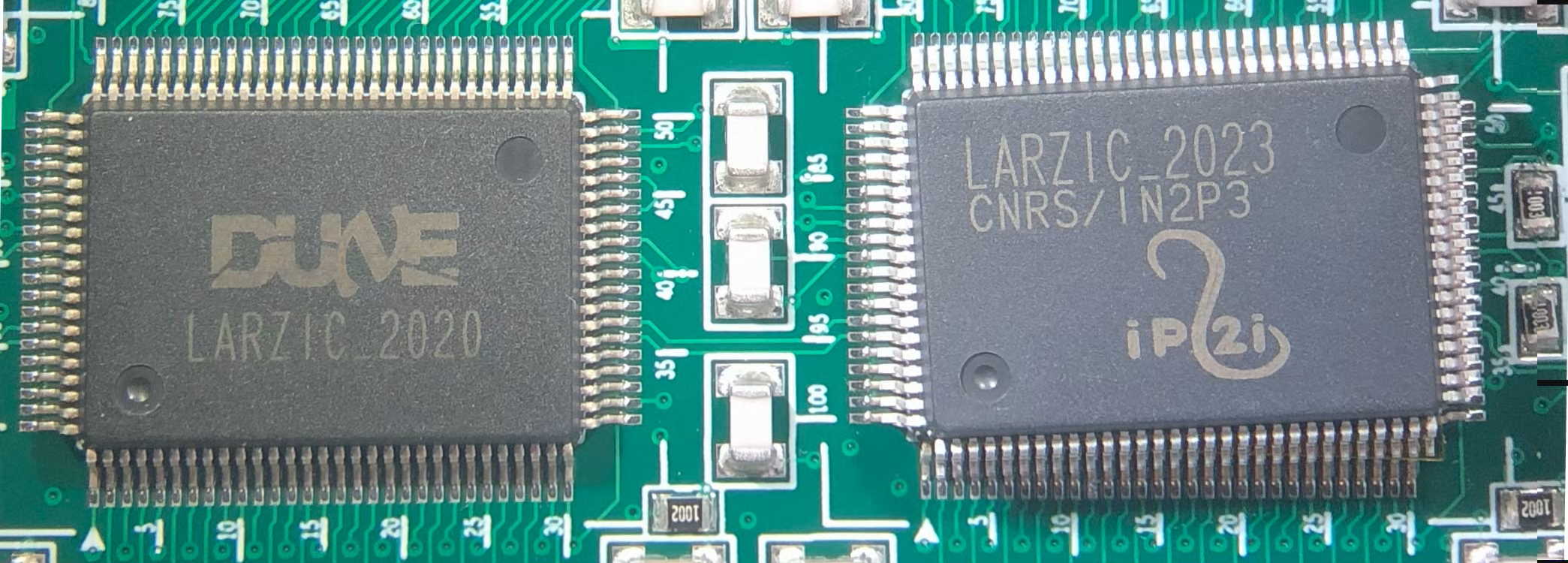

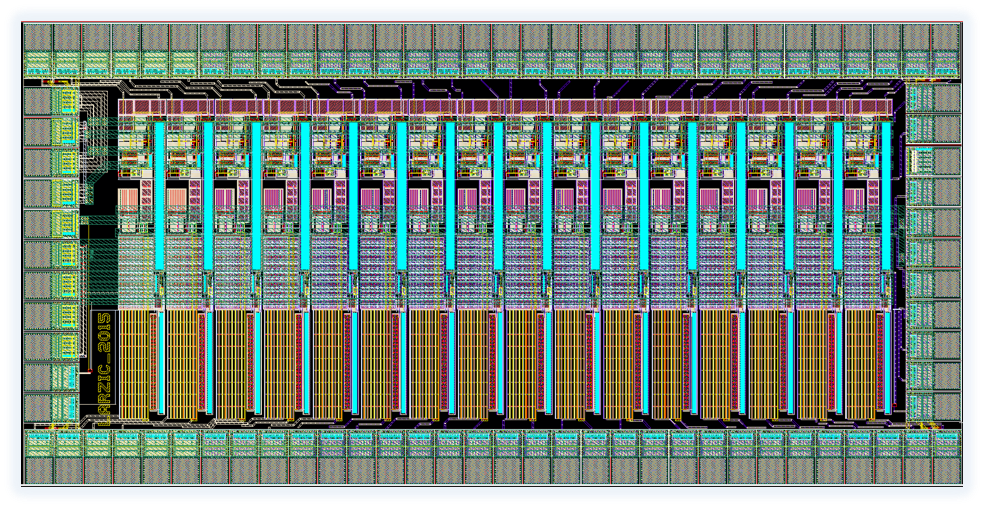

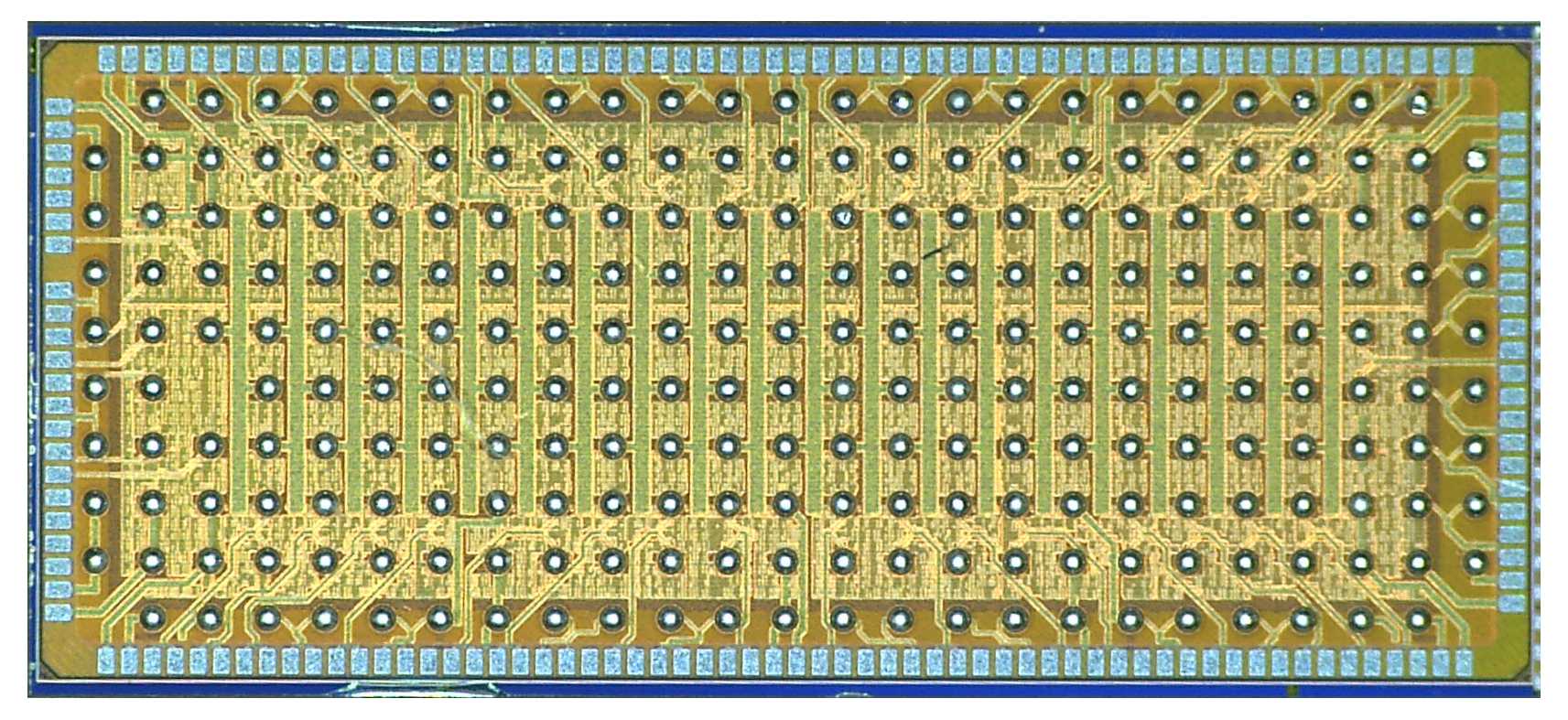

DUNE : LARZIC ASIC

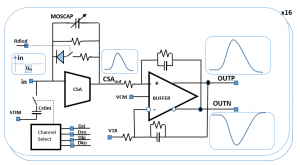

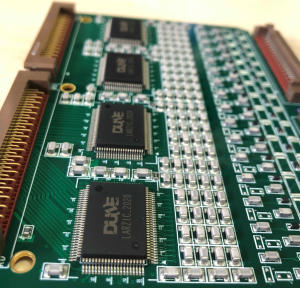

Le circuit LARZIC (Liquid Argon Zygote IC) est un circuit 16-voies capable de mesurer 15000 électrons arrivant durant 500-nanosecondes avec un bruit plancher inférieur à 1000 électrons à -160°C pour une capacité détecteur de l’ordre de 250pF. La performance de diaphonie entre voies est inférieur à 1%. Après deux pré-production en 2015 et 2020, il a été produit à 20000 exemplaires dans le but d’équiper le détecteur lointain à dérive vertical : DUNE VD Far Detector (Vertical Dritf). Le pré-amplificateur de charge est suivi d’un buffer différentiel. La puissance consommé est de 280mW soit 17.5mW/canal pour une tension d’alimentation de 3.3V

Le circuit LARZIC (Liquid Argon Zygote IC) est un circuit 16-voies capable de mesurer 15000 électrons arrivant durant 500-nanosecondes avec un bruit plancher inférieur à 1000 électrons à -160°C pour une capacité détecteur de l’ordre de 250pF. La performance de diaphonie entre voies est inférieur à 1%. Après deux pré-production en 2015 et 2020, il a été produit à 20000 exemplaires dans le but d’équiper le détecteur lointain à dérive vertical : DUNE VD Far Detector (Vertical Dritf). Le pré-amplificateur de charge est suivi d’un buffer différentiel. La puissance consommé est de 280mW soit 17.5mW/canal pour une tension d’alimentation de 3.3V

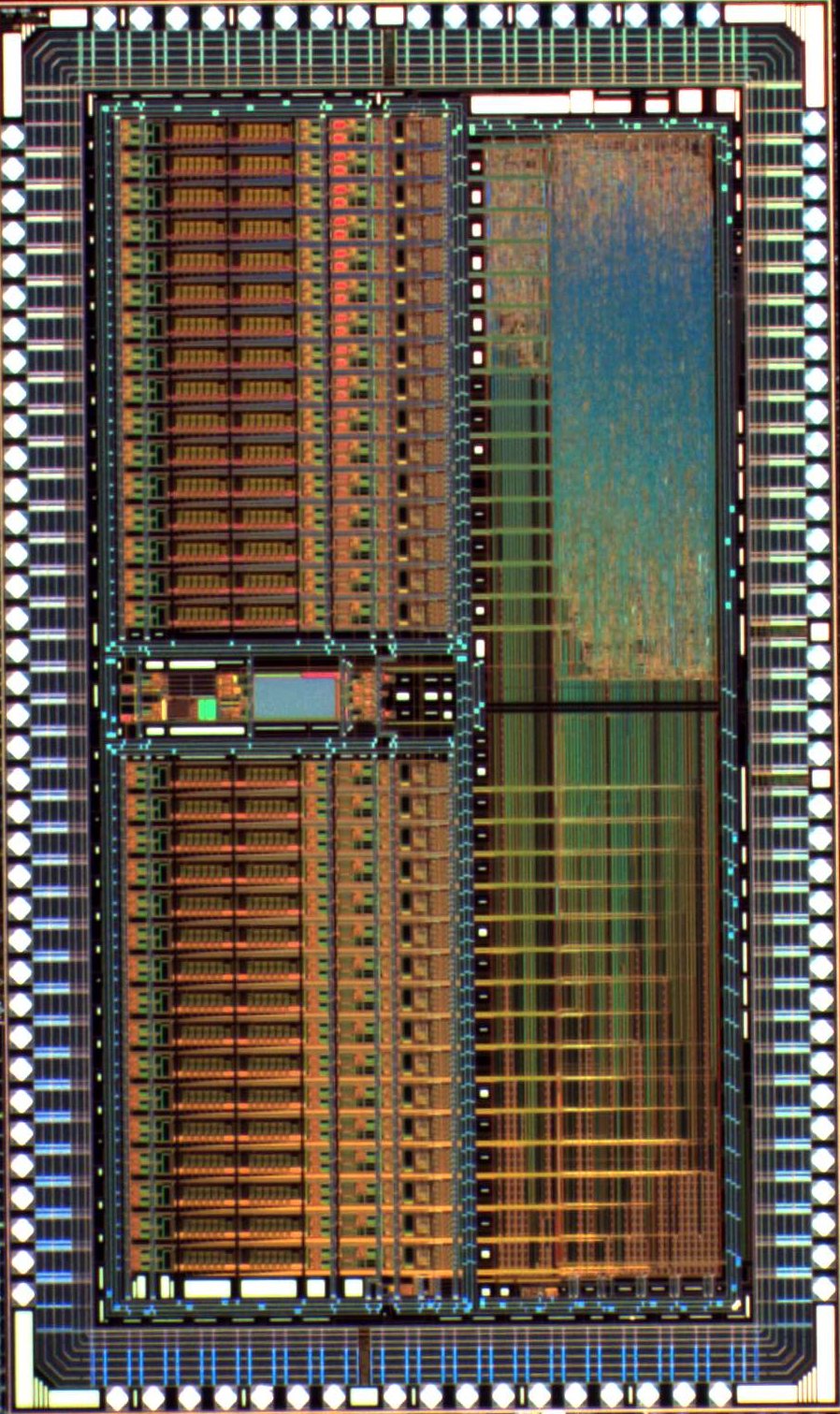

4000 FEB (Front End Board) sont en production. La conception microélectronique de ce circuit en téchnologie 350nm a été entièrement effectué à l’IP2I. Ce circuit a équipé divers détecteurs au CERN tels que proto-Dune (6x6x6 m3), le 3x1x1 m3, et la « cold-box » pour tester le « vertical dritf ». Plus de détail sur l’expérience de physique dans la page Neutrinos.

______________________________________________________________________________________________________

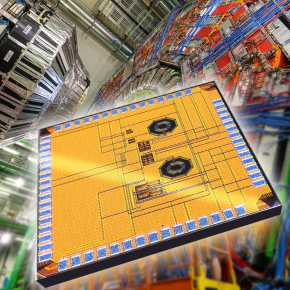

CIC : Concentrateur ASIC for CMS tracker upgrade phase II

Publication/communications sur le CIC :

TWEPP_2018 : https://cds.cern.ch/record/2650712/files/CR2018_278.pdf?version=1

TWEPP_2021: https://dx.doi.org/10.1088/1748-0221/17/05/C05016

Contexte scientifique :

CS_IP2I_2020 : https://indico.in2p3.fr/event/22872/sessions/14179/attachments/61623/84085/CMS_CSIP2I_TrackerUpgrade.pdf

EPIGRAPHY 2026 : https://indico.cern.ch/event/1608897/contributions/6805147/attachments/3199205/5695814/CMS_OT_EPIGRAPHY.pdf

R&T FASTIME

Porteur de projet : Mokrane Dahoumane.

laboratoire participant au projet IP2I, IJClab, LP2iB, LPC-caen, LPCA, OMEGA.

Les membres du projet FASTIME (24 personnes depuis le début du projet):

Ludovic Alvado, Nicolas Arveuf, Roméo Bonnefoy, Raphael Bouet, Luigi Caponetto, Xiushan Chen, Amal Contamine, Sébastien Drouet, Frédéric Druillole, Christian Fayard, Imad Laktineh, Frédéric Jouve, Laurent Leterrier, Samuel Manen, Hervé Mathez, Marie-Lise Mercier, Maxime Morenas, Allaoui Mhoudini, Ludovic Raux, Patrice Russo, Christophe Sylvia, Philippe Vallerand, Richard Vandaele, Mokrane Dahoumane.

Contexte :

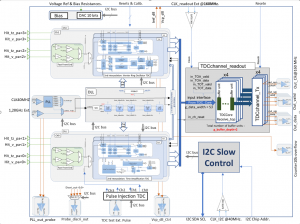

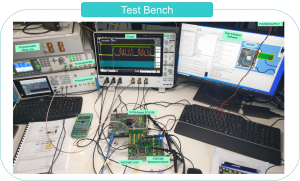

FASTIME est un projet de R&T/IN2P3 démarré en janvier 2021 qui porte sur le développement d’une électronique intégrée (ASIC) de mesure de temps très rapide de résolution de l’ordre de la picoseconde. Une telle résolution devient de plus en plus nécessaire dans de nombreux domaines : par exemple, dans les futures expériences de physique des particules pour réduire le pile-up de ~1000, ou dans les futures générations d’imagerie médicale (TEP) pour réduire de ~20 la dose injectée dans les patients ou enfin pour d’autres applications sociétales (détecteurs pixels précis dans le temps) dont la résolution temporelle inférieure à 1 ps rms ne doit pas être dégradée par l’électronique de lecture. Cette proposition s’appuie sur l’expertise et sur la synergie de plusieurs laboratoires de l’IN2P3 et offre ainsi un cadre collaboratif pour proposer des solutions novatrices et murir une technologie porteuse au-delà de l’existant.

L’objectif de ce projet est de réaliser un prototype d’ASIC multivoies qui intègre une chaine complète de la mesure de temps en deux phases principales. Pour la réalisation physique du circuit, nous avons sélectionné la technologie TSMC 130nm pour sa maturité et sa pérennité, ses performances et sa grande tenue aux radiations validée par le CERN. Ce choix technologique a également été motivé par l’expertise de la communauté IN2P3 dans cette technologie nous permettant de s’appuyer sur des bases solides. Le transfert de ce design vers des technologies plus fines, comme la TSMC 65nm ou la FD-SOI 28 nm, restera réalisable au sein du/des projets de R&T après FASTIME.

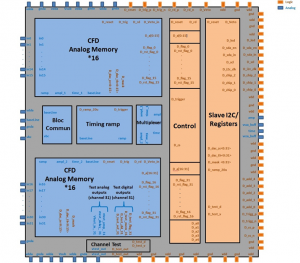

Le premier étage de la chaine intégrée dans FASTIME, L’étage de Front-End, comporte deux architectures de préamplificateurs rapides (un préampli à transimpédance et un préampli en tension) et un discriminateur avec 1 ps rms de résolution pour une charge de 1 pC. L’étage TDC est composé de deux niveaux d’interpolation offrant une précision globale de 1 ps rms. Une DLL avec un pas de quantification de 24 ps constitue le 1er étage d’interpolation. Le résidu de cette mesure est extrait par un bloc spécifique et est envoyé sur un 2ème étage d’interpolation réalisé avec deux architectures différentes : un TDC à Vernier Ring Oscillateur et un TDC à Amplificateur de Temps, avec 3 ps de LSB chacun (0.86 ps rms de bruit de quantification). Tous les paramètres du chip sont configurables par I2C (slow control). Les data de la mesure sont sérialisées et sorties en différentiel grâce à un circuit SLVS.

Cette R&T nous a permis de faire une étude comparative entre les différentes options intégrées. Les résultats des tests électriques du circuit sont très encourageants et ont fait l’objet de présentation Poster à la conférence IEEE NSSMIC-RTSD 2024. Des tests approfondis sont en cours et se poursuivront jusqu’à fin juin 2025. Toutes les fonctionnalités du circuit ont été validés avec succès. Le jitter du Font-End visualisé au scope est de 3 ps rms ; ce résultat, même très proche des spécifications, est détérioré par les éléments parasites de visualisation. Le jitter propre de la chaine complète sur sa sortie numérisée, dont les résultats attendus pour fin mars, devra être meilleur que 3 ps rms. Plusieurs mesures intermédiaires ont été réalisées avec succès telles que : calibration du TDC Vernier, Test de la PLL intégrée, test de la DLL etc… La documentation technique est systématiquement rédigée à chaque étape de travail dans le projet. Les résultats et les études seront publiés dans un journal. Le projet prendra fin le 31 décembre 2025.

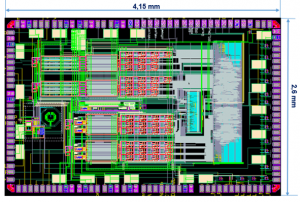

PICMIC

Le projet PICMIC est un nouveau type de détecteur mesurant à la picoseconde un évènement et au micromètre près sa position. Dans un système sous vide, une particule déclenche une avalanche dans un MCP (Micro Chanel Plate) qui vient être absorbé par un circuit dédié : PICMIC-0. L’ASIC PICMIC-0 interconnecte des pistes d’hexagones de 5µm dans trois directions pour 2556 voies de lecture sur une surface de 0.5cm². L’ASIC PICMIC-1 en cours de production intègre un nouvel amplificateur de charge, un système de lecture parallèle des colonnes, une PLL, et 5112 voies de lectures pour une surface active de 1.9cm².

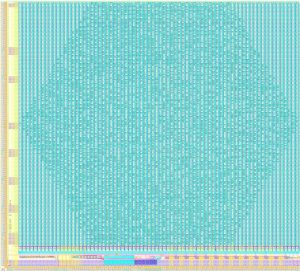

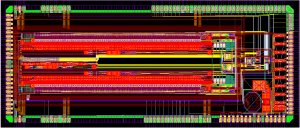

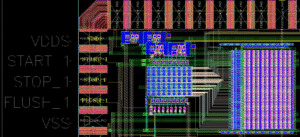

ASIC PICMIC-0 die picture (gauche) ASIC PICMIC-1 layout view (droite)

Précédentes présentations de PICMIC-0 :

FCPPN/L_2025 : https://indico.ihep.ac.cn/event/25400/contributions/195672/ VCI_2025 : https://indico.cern.ch/event/1386009/contributions/6279064/ JMi2i_2024 : https://indico.in2p3.fr/event/33980/contributions/144067/ FCPPN/L_2024 : https://indico.in2p3.fr/event/20434/contributions/140589/ TWEPP_2023 : https://indico.cern.ch/event/1255624/contributions/5443787/

TIIX

TIIX est un projet en collaboration avec le laboratoire IPHC de Strasbourg. C’est une évolution du projet TIIMM-EU-STRONG2020 et il porte sur le développement d’un détecteur MAPS (capteur monolithique à pixels actifs) pour le suivi de précision et l’identification de particules en hadronthérapie.

Dans des applications médicales, notamment en hadronthérapie et en radiodiagnostic, les détecteurs de suivi de particules conçus pour identifier et suivre les ions de faible énergie sont largement utilisés pour surveiller, contrôler et étudier l’interaction de faisceaux d’ions soigneusement dirigés avec le corps humain. La technologie des capteurs à pixels actifs monolithiques est un choix judicieux pour ces détecteurs, notamment lorsque la minimisation de la diffusion multiple, des pertes d’énergie et des interactions des particules incidentes est essentielle.

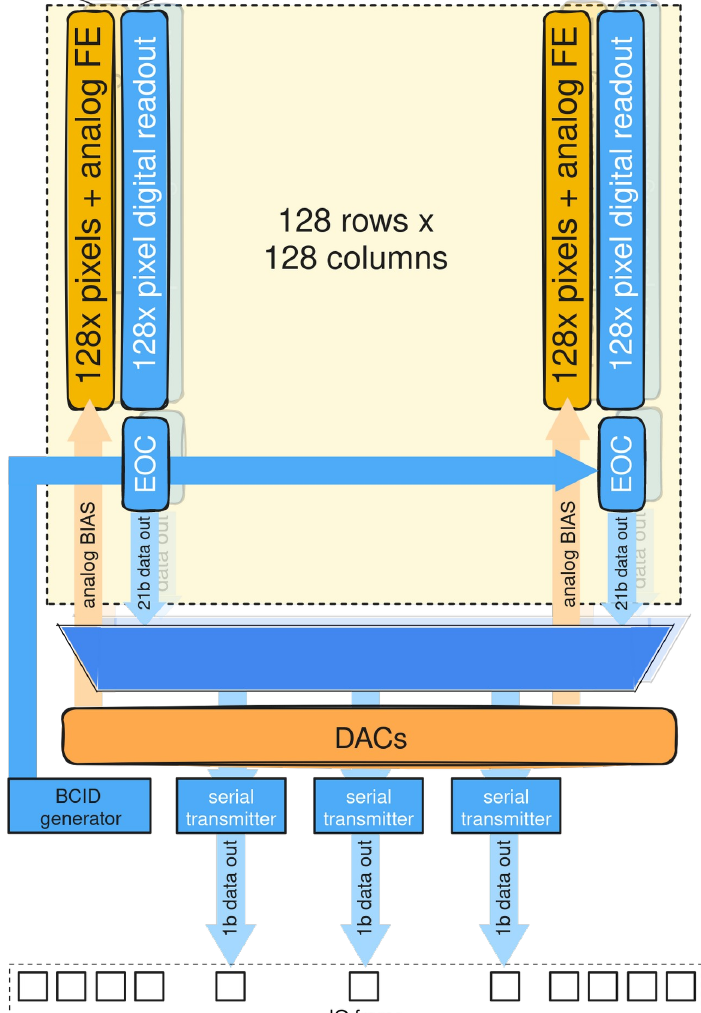

L’objectif de ce projet est de développer un détecteur MAPS pour le suivi de la position des particules de haute précision (< 10 μm) et l’identification des particules par des mesures de perte d’énergie (ΔE: 5 keV à 5 MeV). Il est composé d’une matrice de 128 x 128 pixels avec un pitch de 42 μm et un time-stamps local d’une précision de 25 ns, permettant l’estimation de l’énergie des particules incidentes grâce à une mesure de la charge libérée par pixels avec une résolution de 10 bits.

L’architecture de lecture implémentée se base sur un mécanisme de type column-drain avec le passage d’un token, un multiplexeur et un sérialiseur. Chaque pixel est équipé d’un amplificateur sensible à la charge avec une large plage d’entrée dynamique, d’un comparateur à seuil variable et d’une unité de lecture numérique. La logique numérique intégrée au pixel est déclenchée par un détecteur de front qui génère des impulsions sur les fronts avant et arrière de la sortie du comparateur. Un timestamp de 4 bits (BCID) est verrouillé à chaque front et stocké dans deux mémoires distinctes intégrées au pixel jusqu’à sa lecture, permettant ainsi une mesure de dépassement de seuil (ToT). Le BCID est distribué avec un intervalle sélectionnable de 25 ns (ou 50 ns), offrant des fenêtres temporelles maximales de 400 ns (ou 800 ns). L’utilisation de deux mémoires à 4 bits intégrées au pixel réduit la surface occupée par la logique numérique, permettant ainsi la lecture numérique de l’ensemble de la colonne à l’aide de standard-cells numériques. Un signal de token est généré par chaque pixel lors d’une écriture en mémoire. Les données sont lues de manière asynchrone depuis le bas de chaque colonne, et les pixels ayant émis un token sont ensuite lus selon une priorité fixe de haut en bas. Une extension dynamique de 4 à 10 bits est implémentée en périphérie afin d’améliorer la plage dynamique du ToT à 1:1000. Trois sérialiseurs de sortie transmettent les données d’événement hors puce à 160 Mbit/s, le ToT final étant calculé comme la différence entre les temps d’arrivée des fronts avant et arrière de chaque occurrence. La conception adopte une stratégie « Digital on Top », avec une implémentation standard du bloc numérique par cellules et une vérification à l’aide de la méthodologie de vérification universelle (UVM). La soumission de l’ASIC au processus Tower 180 nm est prévue pour fin année 2025.

Lojic130

Le but de cette PLL est de développer un générateur d’horloge interne adapté aux développements d’ASIC qui intègrent une mesure de temps ou qui nécessitent une horloge interne de l’ordre du GHz.

Pour les futurs up-grade des expériences CMS et ATLAS au CERN, la mesure de temps devient un élément déterminant qui permettra de réduire le flot de données et d’améliorer la précision spatiale du point d’interaction. Une précision de 10 ps induit une résolution spatiale de 3 mm. Pour les mêmes raisons, les développements en imagerie médicale sont aussi intéressés par la mesure de temps. Des applications basées sur une mesure de temps de vol (ToF) nécessitent également des précisions autour de 10 ps.

IN2P3 : https://www.in2p3.cnrs.fr/fr/cnrsinfo/hl-lhc-lin2p3-fait-ses-premiers-pas-dans-les-detecteurs-4d

Papier Jinst : https://iopscience.iop.org/article/10.1088/1748-0221/17/05/T05014

R&T SiGe

D. Charrier Subatech – porteur, D. Prêle APC – co, L. Alvado LPC Caen, E. Bechetoille IP2I, S. Chen APC, L. Leterrier LPC Caen, J. Mesquida APC, P. Russo IP2I, B. Ton APC, M. Gonzalez APC

Objectif technique de la R&T :

L’objectif technique de ce projet de R&T est multiple :

Créer des fonctions « brique de base » bien identifiées en technologie BiCMOS et en particulier là où les technologies CMOS, même avec des nœuds de 28nm, montrent leurs limites tel que : Dynamique en tension et en courant, Bruit basse fréquence et bruit sur basse impédance, Produit gain-bande et temps de monté en grand signal, Performances à température cryogéniques.

Les technologies de microélectroniques et les outils logiciel de vérification se complexifiant avec le temps, il est indispensable d’éviter la dispersion en se concentrant sur une ou deux technologies de référence. Elles seront sélectionnées par ce projet en fonction des performances exigées, de la pérennité estimée, de la facilité d’accès au fondeur et du coût. L’une des technologies, la ST130nm SiGe a déjà été évaluée et retenue par l’APC.

Créer l’environnement nécessaire au partage de briques de base et à l’accès à la technologie choisie est un enjeu majeur de ce projet. Pour cela, on se donne comme objectif de documenter les réalisations sur une plateforme tel que la forge ou ATRIUM.

Objectif scientifique de la R&T :

Ce projet de R&T est avant tout une R&T transverse. Elle n’a pas vocation à développer des ASICs pour des expériences de physique identifiées mais plutôt pour des familles de détecteurs où des types de fonctions.

Les performances des transistors bipolaires étant élevées à basse température, à basse fréquence et à basse impédance, cette technologie est particulièrement pertinente en Astroparticule sur des détecteurs bolométriques ou cryogéniques à base de SQUID, TES mais aussi en physique nucléaire sur des détecteur Germanium refroidis ou sur des TPC à xénon liquide.

Les transistors bipolaires sont par nature idéaux pour concevoir des amplificateurs trans-impédance très large bande et bas bruit, ce qui est un atout pour les détecteurs diamants utilisés par exemple pour du contrôle de faisceau sur les accélérateurs.

Les besoins des futures expériences de l’IN2P3 garderont toujours un besoin fort en analogique front-end. Dans le même temps, beaucoup de design ASIC évoluent vers toujours plus de numérique justifiant le recours à des techno-fine full CMOS. Cependant, afin de garder des technologies a même de répondre à des performances analogiques couplé à un détecteur spécifique, il est important de garder au moins une technologie mature BiCMOS et généraliste. En effet, nombres de détecteurs de physique nucléaire appliquée au médical ont davantage besoin de dynamique que de densité d’intégration.

Réalisations :

Un ASIC a été envoyé en fonderie en 07/2024. L’ASIC va être testé prochainement. L’ASIC est composé de différents blocs :

– Amplificateur de tension différentielle (contribution IP2I)

– Thermomètre

– Amplificateur rail à rail en entrée et en sortie

– Pré-amplificateur bas bruit large bande à grande dynamique (TIA :Trans-impedance Amplifier)

Reference / communication :

https://indico.in2p3.fr/event/27936/contributions/114099/attachments/78507/114566/RetT_BiCMOS_JME_Caen.pdf

https://caemi2i.in2p3.fr/wp-content/uploads/2024/09/RetT_BiCMOS_IHP130_DC-comp.pdf

https://mi2i.in2p3.fr/index.php/les-groupes-et-cellules/

https://indico.in2p3.fr/event/26475/contributions/115837/attachments/73415/105395/Lyon-RetT-2022-BiCMOS.pdf

SPIDER: Swift Pipelined DigitizER

Projet mené par l’IJClab le LPCA et le LPC-Caen, dans lequel nous avons une contribution.

Présentation passée du projet:

Publication 2026 :http://arxiv.org/abs/2512.17355

JME2025 Spider présentation (indico IN2P3 restricted)

DRD Calo 2025

GDR Di2i 2024

JME2023 Spider présentation

Xtract

Réalisé en collaboration avec le LPCA et l’IP2I de 2014 à 2018.

Afin de reconstruire en 3 dimensions la position des interactions qui ont lieu dans la chambre à projection temporelle de XEMIS 2 en utilisant l’effet Compton, il est important de connaitre avec exactitude le temps auquel elles se produisent et l’énergie qu’elles déposent. L’ASIC XTRACT a pour mission d’extraire ces deux informations des signaux issus de l’ASIC IDeF-X LXe, sans besoin de faire l’acquisition d’un nombre important de points, autour de la zone d’intérêt, pour obtenir ces informations par le biais d’un traitement informatique idoine postérieur. Il offre ainsi la possibilité de réduire considérablement la quantité de données sortant de XEMIS 2 en ne mémorisant que les données importantes. Le nom XTRACT signifie XEMIS TPC Readout for Extraction of Charge and Time.

Ref :

numéro de brevet: WO2018158315

https://indico.in2p3.fr/event/14305/attachments/14694/18007/soulier_poster_xtract.pd

MPTDC

MPTDC : Multiphase Time to Digital Converter.

TSMC130nm

2.5ns range 17ps LSB with 7.02psRMS resolution with 9 phase offline time calculation

Le savoir-faire du service Microélectronique de l’IP2I et plus généralement de l’IN2P3 peut se résumer de manière non exhaustive à la conception et/ou à l’intégration de bloc tels que :

- Préamplificateurs de charge et de courant,

- Circuits de conversion numérique vers analogique (DAC),

- Circuits de conversion analogique vers numérique (ADC),

- Étiqueteurs en temps (TDC),

- Boucle à verrouillage de phase (PLL),

- Régulateurs de tensions (LDO),

- Références de tension stables en températures (Bandgap),

- Mémoire (flash, SRAM…),

- Diodes,

- Filtres,

- Multiplexeurs,

- Circuits de protection.

- Implémentation de processeurs RiscV

La conception intégrée de circuits électronique nécessite la maitrise des outils de conception tels que la suite Cadence © (virtuoso, spectre, pvs, innovus, genus, tempus, liberate…) pour réaliser les simulations et l’implantation du dessin des masques.

Au cours des différents projets et suivant les besoins, les concepteurs ont utilisé des technologies variées tels qu’AMS, ST, IBM, TSMC, TowerJazz, dans des nœuds technologies passant par les dimensions minimales de largeur de transistors de 350nm, 130nm ou encore 65nm.

Représentation graphique des spécificités demandées aux circuits pour la physique des particules.